# **MEMS** Micropackaging for Microsystems Integration

Sazzadur Chowdhury, G. A. Jullien, M. Ahmadi, W. C. Miller

**Research Centre for Integrated Microsystems** Department of Electrical and Computer Engineering University of Windsor Windsor, Ontario, N9B 3P4, Canada

### Abstract

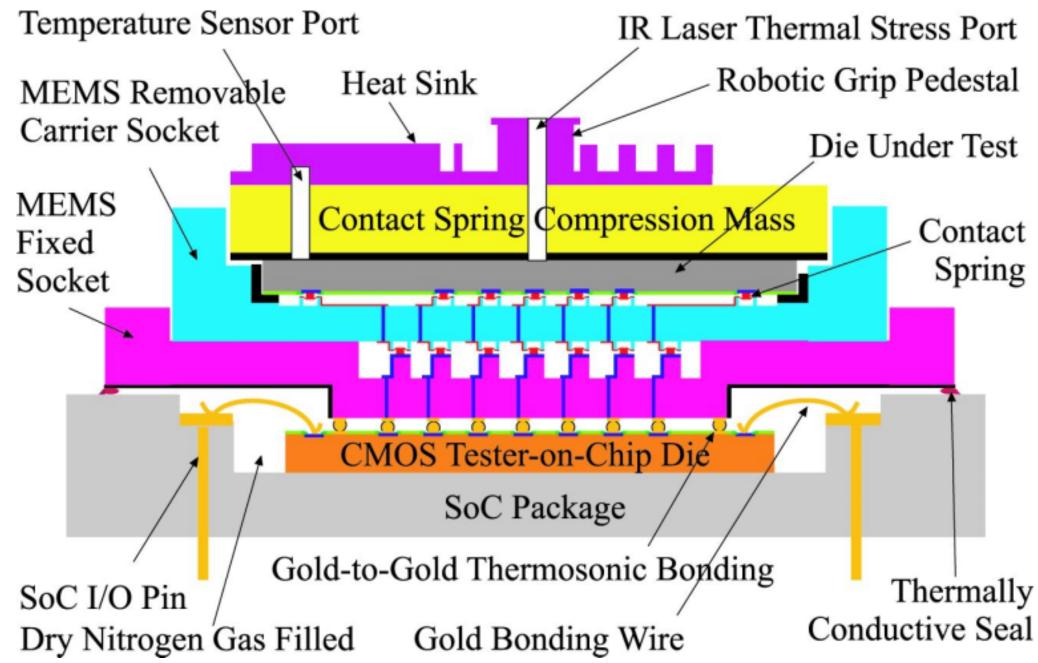

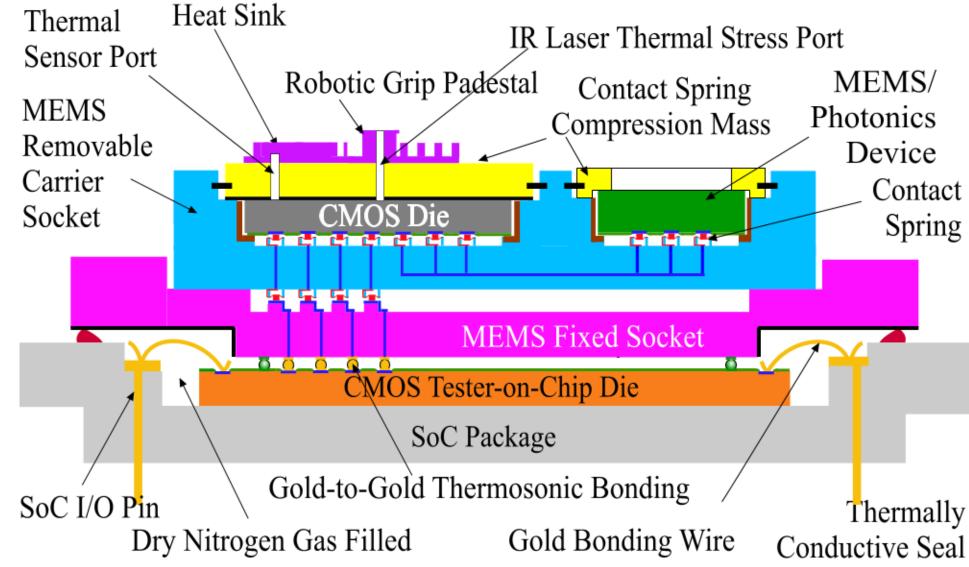

- A modular MEMS socket system has been developed that enables a custom, application-specific micropackaging solution for diverse technology dies and devices

- Each socket submodule may contain a CMOS or non-CMOS die (MEMS, Photonics, RF, GaAs, BJT, etc.) or may itself be a sensor/actuator or microanalyzer

- An insertable/removable MEMS microbus card provides connectivity among socket submodules and slides into an interconnection channel prefabricated in all submodules

- The system can also be configured for testing of high density I/O SoC dies or diverse-technology systems using a solderless, pressure dependent cantilevered bridge-type microspring contact mechanism

# **MEMS Micropackaging Solution: Major Design Features**

- A complete working system in a package offering diverse micropackaging solutions

- Scalable single or modular micropackaging  $\bullet$

- Permanent or temporary submodule integration

- Socket submodules to accommodate integrated circuit dies in custom fabricated housing pits

- A sensor can itself be a socket submodule or can be surface mounted in a socket submodule  $\bullet$

- An insertable/removable microbus card provides custom inter-modular connectivity

- Heat deformed, gold coated cantilever microsprings on the microbus card connects to platinum coated microrail contacts inside the vertical interconnection channel in a submodule

- Gold wire bonding between Socket metal pads and die I/O pads

- Low impedance connectivity path

- Conduction type thermal management  $\bullet$

- Cantilevered bridge-type microspring contact enables dies testing

- Easily modifiable connectivity using microbus card

- Batch fabrication using MEMS technology  $\bullet$

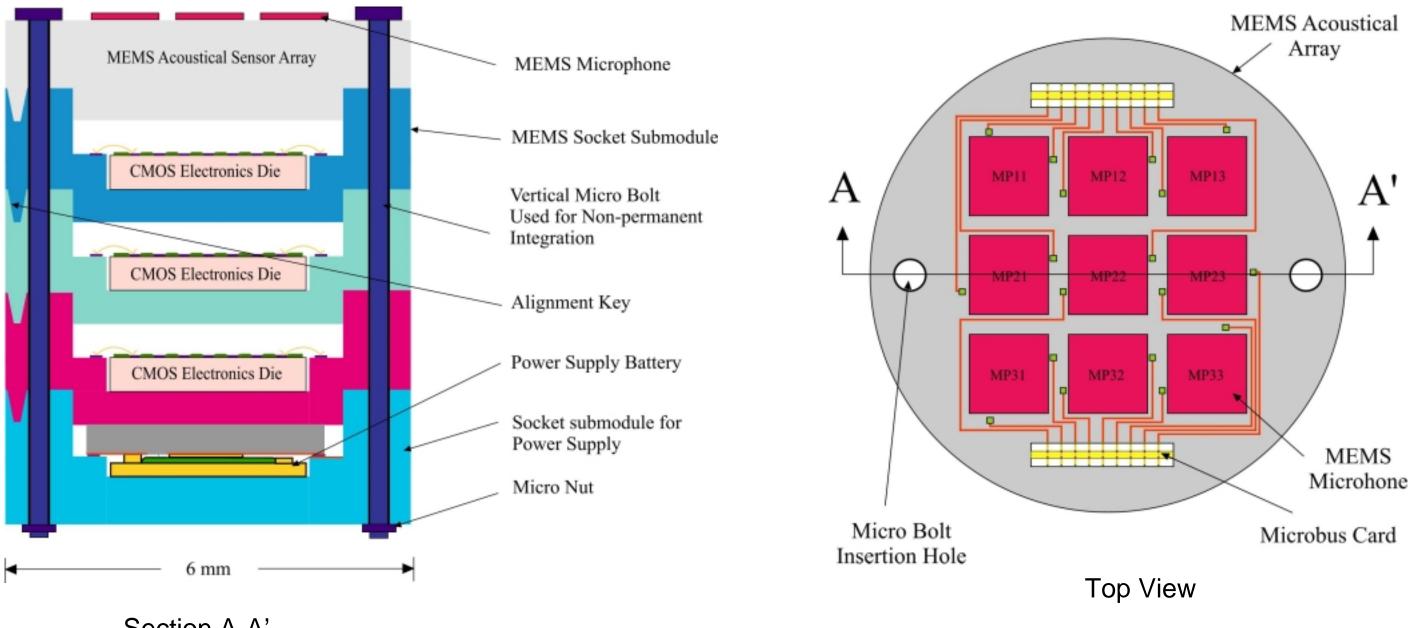

## **Illustration of Modular Integration of a MEMS Sensor and SoC Dies**

Section A-A'

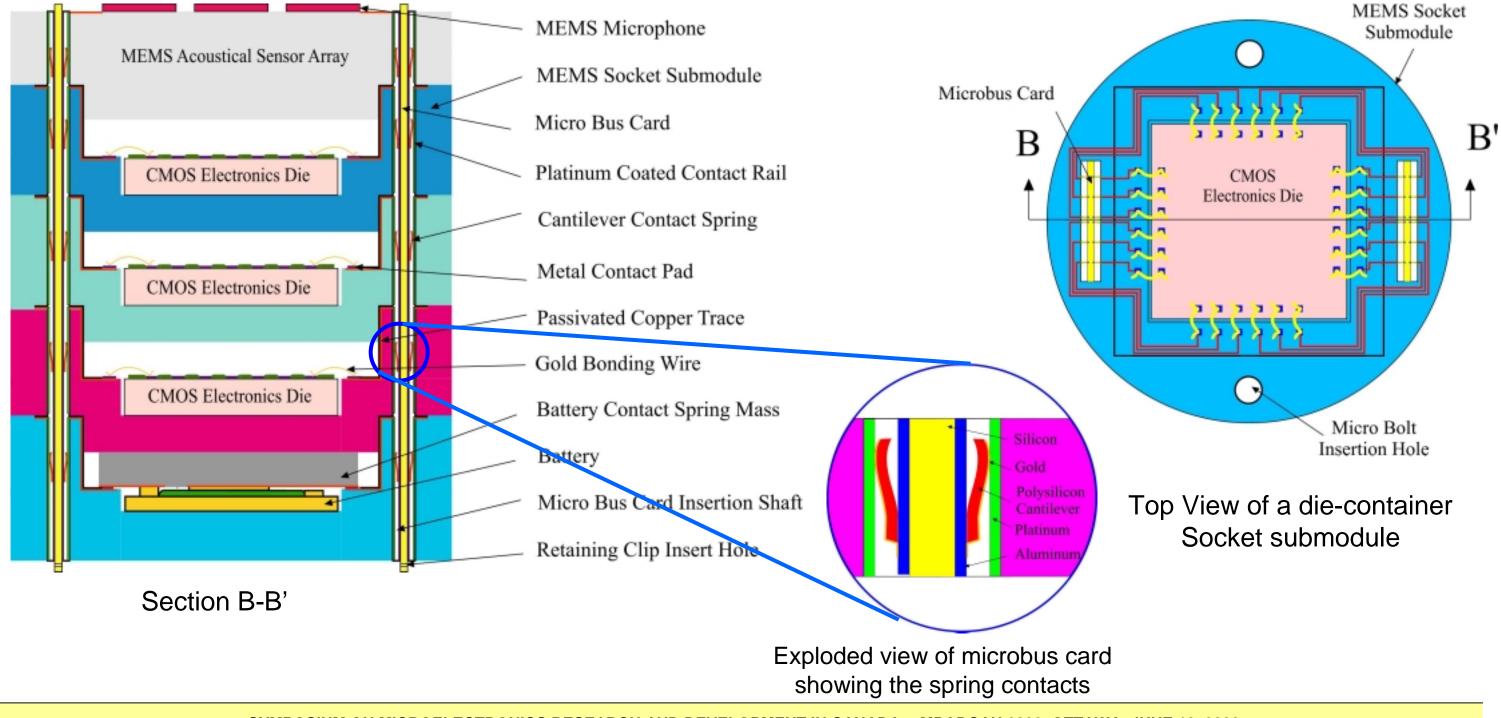

## **Illustration of Microbus Card Connectivity** for Various Submodules

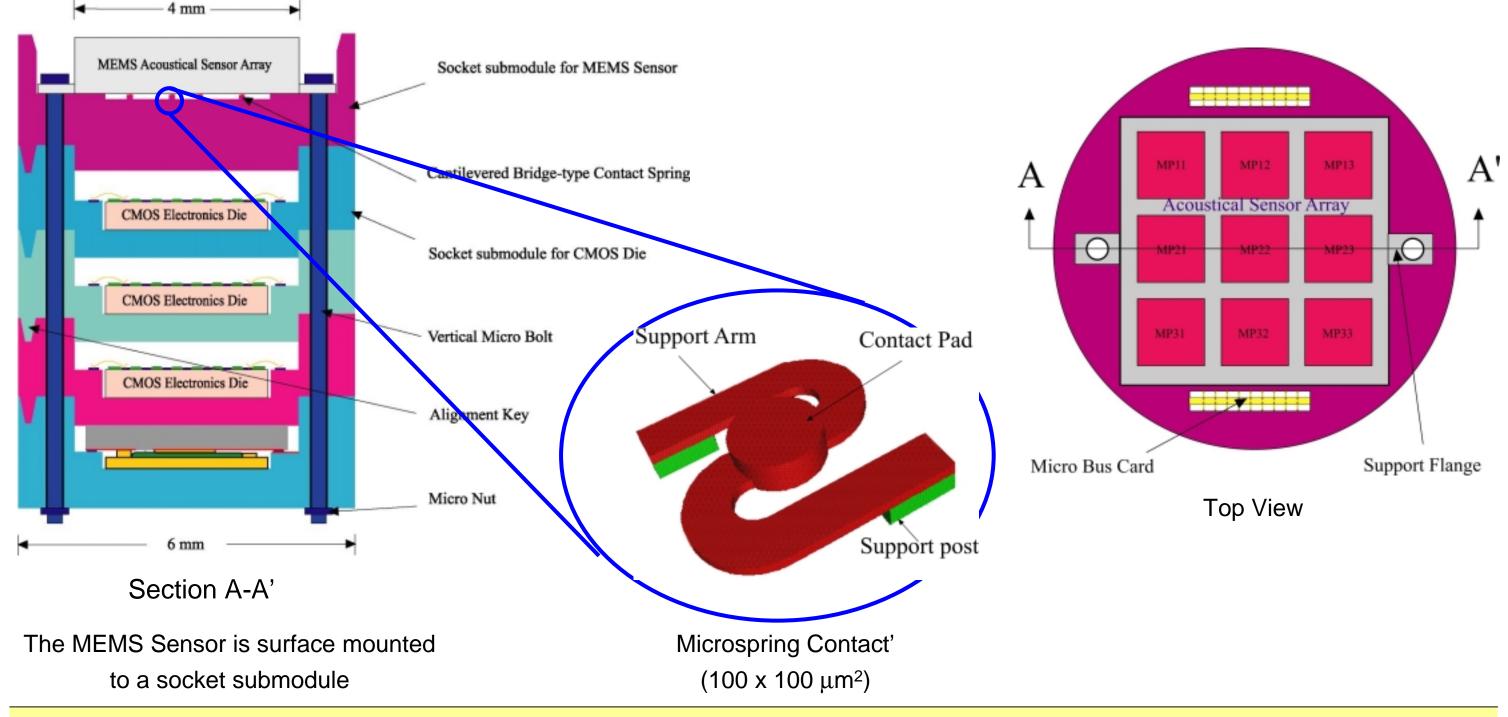

# **Illustration of Temporary Connectivity Using Z-Shaped Microspring Contacts**

┖ᡃ┙┖╋╸

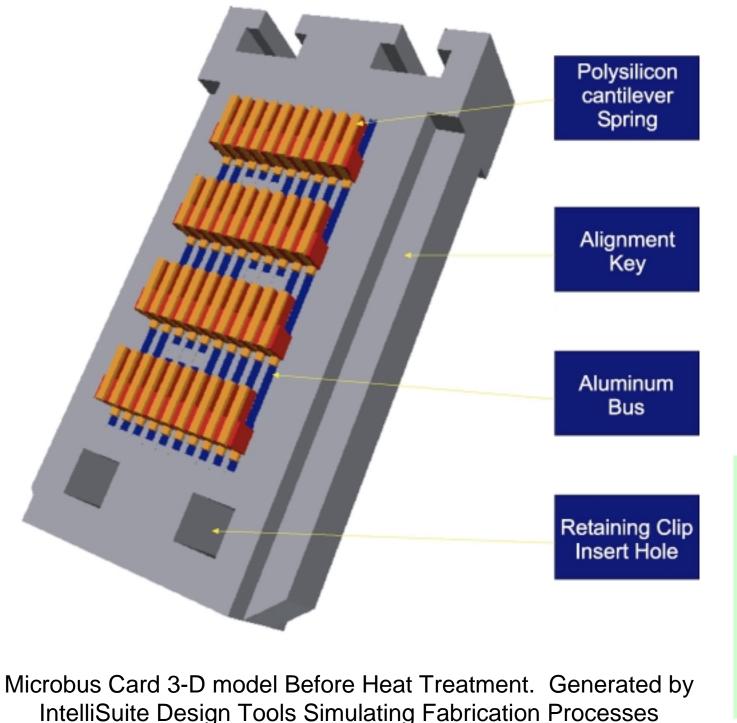

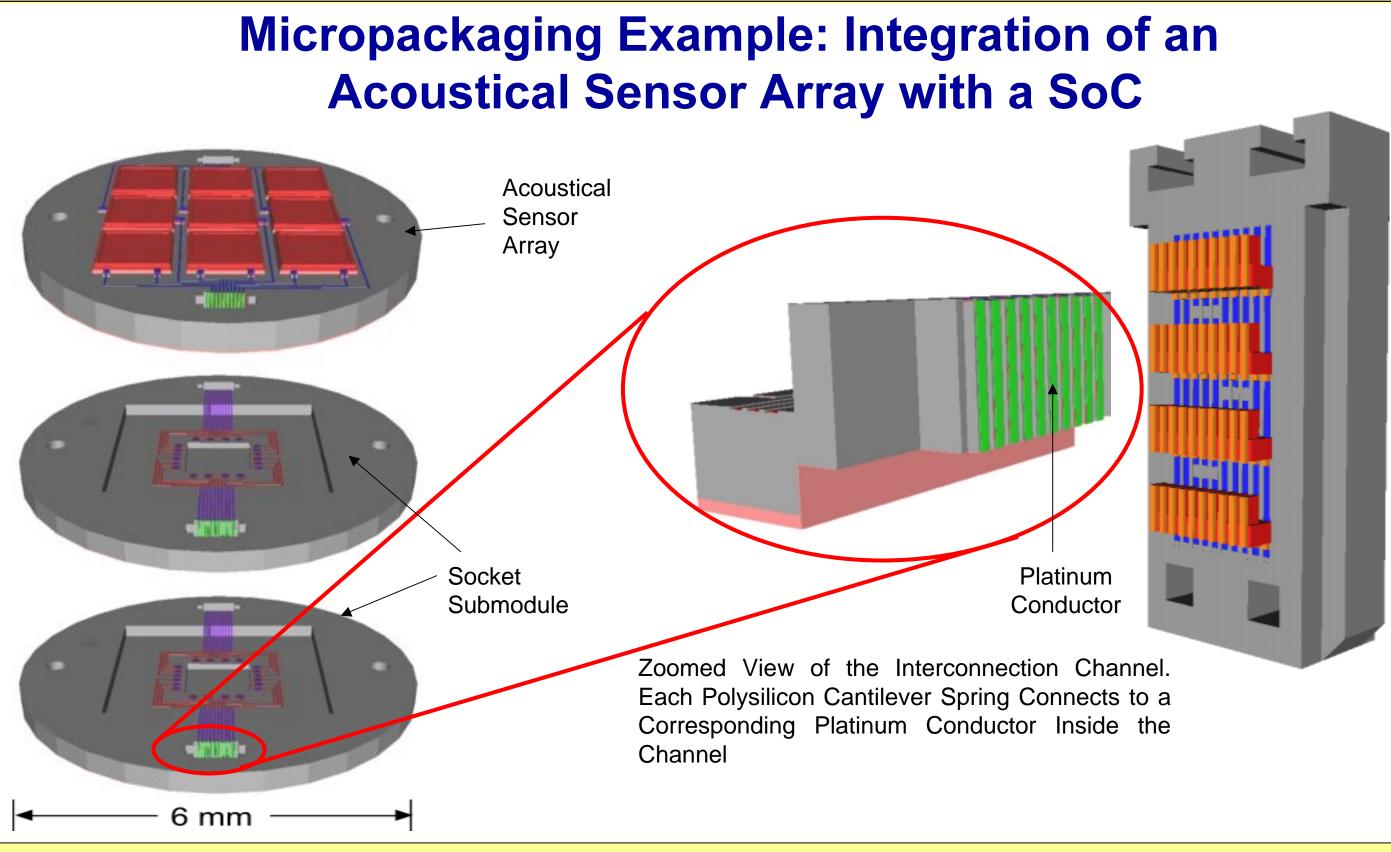

### **Microbus Card Connectivity System**

- The microbus card establishes Inter-modular connectivity when shoved in through an interconnection channel that is present in each socket submodule

- The microbus card is fabricated using MEMS technology

- The gold coated polysilicon cantilevers are heat treated after fabrication at 150-200° C to induce tensile stress so that the cantilevers bend upwards

- When shoved in, the bent cantilevers come in contact with vertical platinum coated interconnection channel and undergo deformation to generate necessary contact force

- Polysilicon Cantilever Dimensions: 100 x 25 x 2 µm

- Gold Conductor Thickness: 200 nm

- Aluminum Bus Dimensions (W/T): 25 x 1 μm

- Retaining Clip Insertion Hole (L/W): 250 x 250 µm

- Microbus Card Dimensions (W/T): 2 mm x 400 μm

- Microbus card Material: Czochralski Silicon

SYMPOSIUM ON MICROELECTRONICS RESEARCH AND DEVELOPMENT IN CANADA MR&DCAN 2002, OTTAWA, JUNE 18, 2002

microrails inside the

**Specifications Major Design**

## **MEMS Socket: Die Container Submodule**

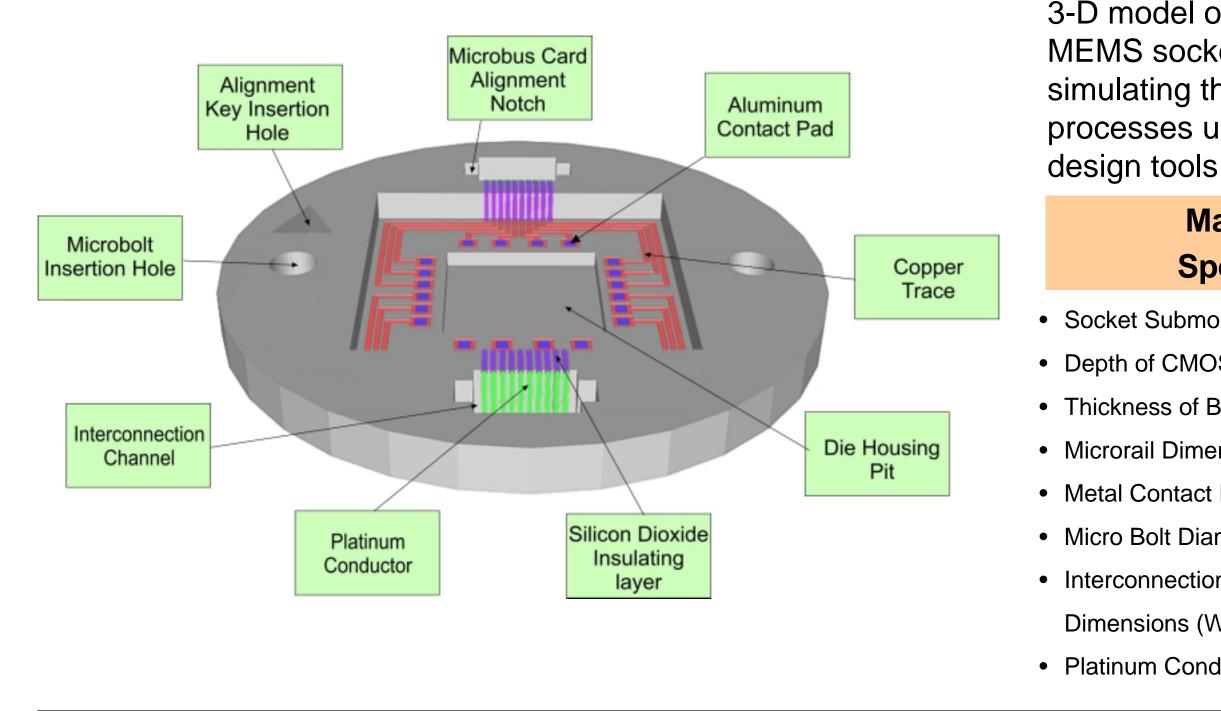

3-D model of a die container type MEMS socket submodule after simulating the fabrication processes using IntelliSuite

### **Major Design Specifications**

• Socket Submodule Thickness : 400 μm Depth of CMOS Die Insertion Pit: 100 µm Thickness of Backside Extrusion: 100 μm Microrail Dimensions (W/H): 25/200 μm Metal Contact Pad Area: 75 x 75 μm Micro Bolt Diameter: 400 μm Interconnection Channel Dimensions (W/T): 2 mm/400 µm Platinum Conductor Thickness: 200 nm

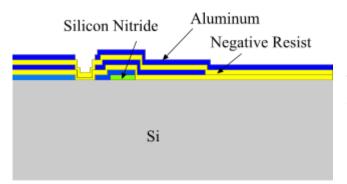

### **MEMS Socket Submodule Fabrication Process**

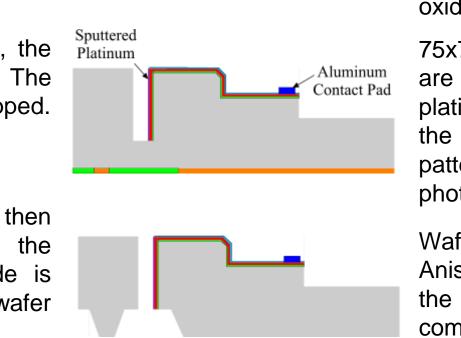

70 nm thick PECVD silicon nitride is deposited, patterned and etched on the top of a 400 µm thick silicon wafer. Three layers of aluminumnegative photoresist laminations are deposited.

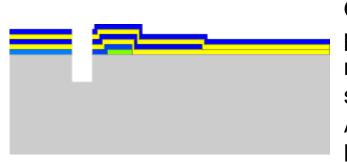

of the  $O_2$  ashing negative photoresist is carried out by ICP-RIE method. The wafer is then successively ICP-RIE etched using Aluminum and negative resist laminations as delayed mask.

After the 3rd ICP-RIE process, the wafer patterning is completed. The 3rd Aluminum mask is then stripped.

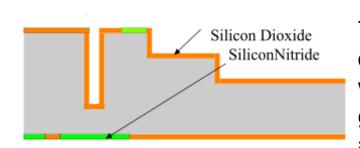

70 nm thick PECVD nitride is then deposited and patterned on the wafer backside. Thermal oxide is grown on both sides of the wafer and patterned.

SYMPOSIUM ON MICROELECTRONICS RESEARCH AND DEVELOPMENT IN CANADA MR&DCAN 2002, OTTAWA, JUNE 18, 2002

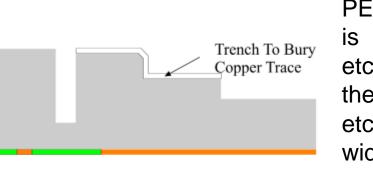

PECVD nitride on the wafer topside is removed. The wafer is TMAH etched to form the slant corner on the top. The wafer is then RIE etched to form 5  $\mu$ m deep by 35  $\mu$ m wide trenches.

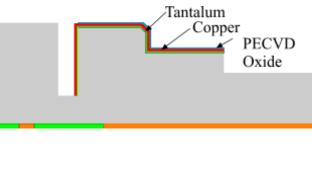

Tantalum is sputter deposited and patterned in the trenches. 1.0 µm thick copper is sputtered and patterned. Finally a 3.5 µm thick silicon dioxide is PECVD deposited to protect the copper traces from oxidation.

75x75 µm<sup>2</sup> Aluminum contact pads are then formed. 200 nm thick platinum is then sputter deposited in interconnection shaft and pattered using an electrodeposited photoresist.

Wafer backside nitride is stripped. Anisotropic etching is performed on the wafer backside using TMAH to complete the fabrication process.

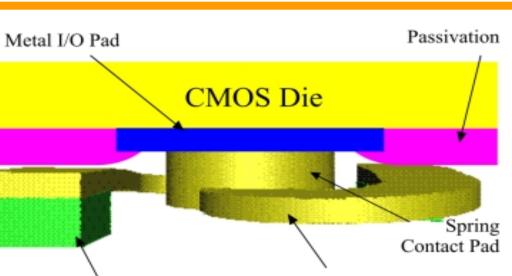

# **CMOS** Die Testing Configuration: Concept

## Multiple Technology Devices or Systems Testing Configuration

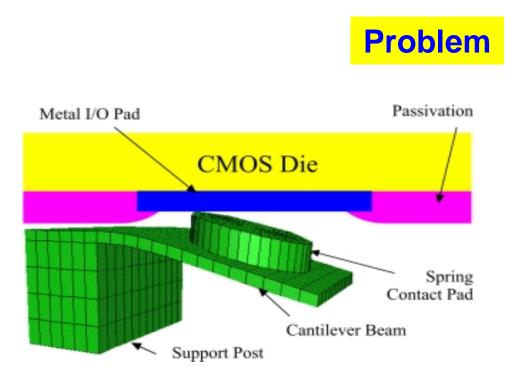

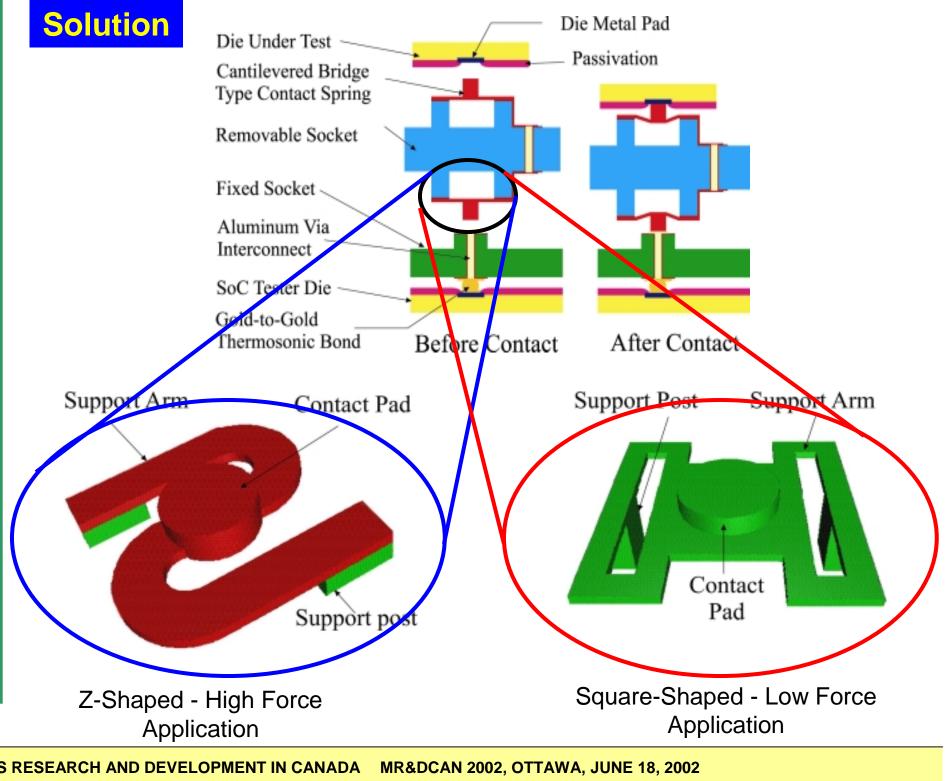

# **Microspring Contact Design Considerations**

- Due to a uniform pressure applied on the top, the contact pad undergoes a torsional deformation that results in a curved top surface

- The whole contact pad surface does not come in contact with the die metal pad

- The result is a higher resistance line-type (arc) contact

SYMPOSIUM ON MICROELECTRONICS RESEARCH AND DEVELOPMENT IN CANADA

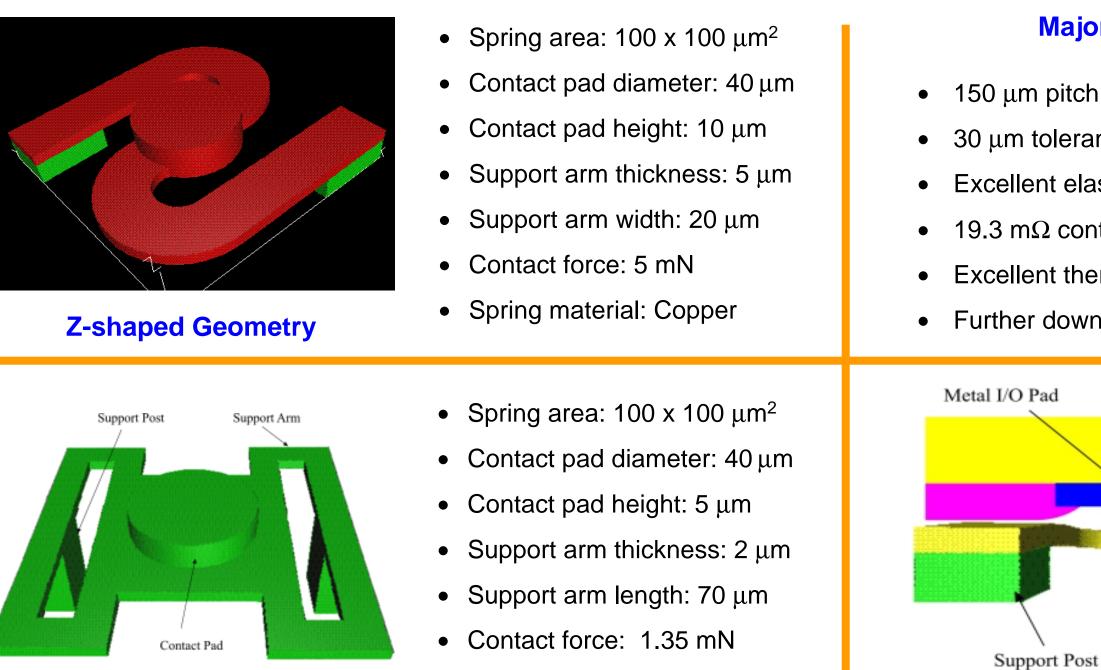

## **Microspring Contact Design specifications**

**Square Geometry**

Spring material: Copper

Support Post

SYMPOSIUM ON MICROELECTRONICS RESEARCH AND DEVELOPMENT IN CANADA MR&DCAN 2002, OTTAWA, JUNE 18, 2002

- **Major Design Features**

- 30 µm tolerance in both X and Y directions

- **Excellent elastic properties**

- 19.3 m $\Omega$  contact resistance

- Excellent thermal properties at 150 ° C

- Further down scalable

Cantilever Support Arm

### **Result: Excellent Connectivity**

ݮ┓ݮ **RESEARCH CENTRE FOR INTEGRATED MICROSYSTEMS - UNIVERSITY OF WINDSOR**

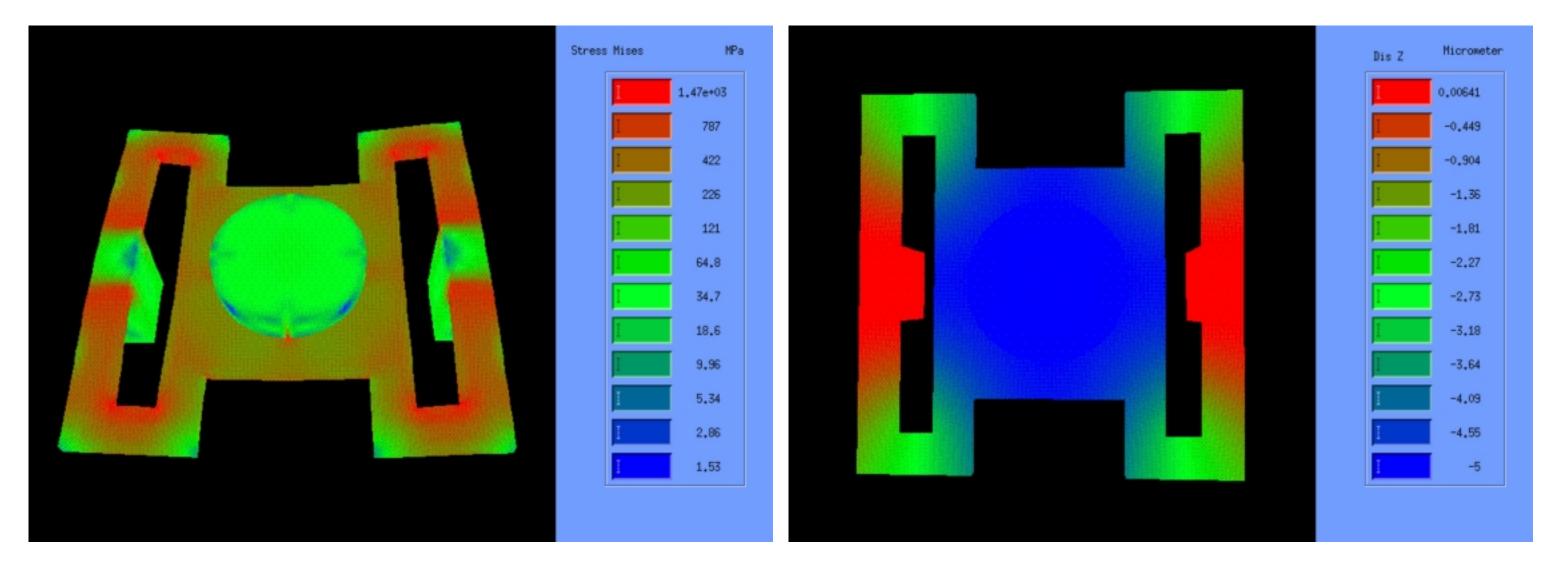

## FEA Simulation Results: Square-Shaped Microspring Contact

Von Mises stress (Max. 1.47 GPa)

Z-axis displacement is uniform throughout the contact pad area

The Von Mises stress is within the elastic limit of copper with a reasonable safety margin for the desired Z-axis displacement Applied force: 1.35 mN Max. Z-axis displacement: 5 µm

┗┓┖┓ **RESEARCH CENTRE FOR INTEGRATED MICROSYSTEMS - UNIVERSITY OF WINDSOR**

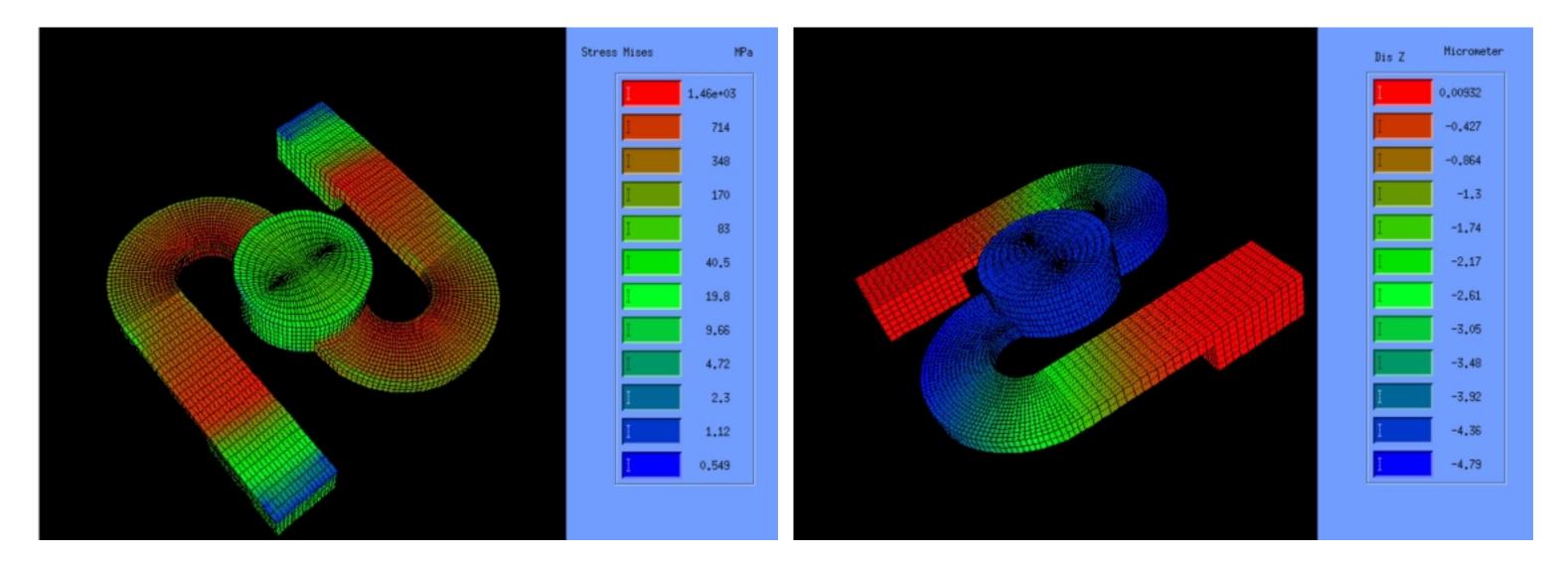

## **FEA Simulation Results: Z-shaped Microspring Contact**

Von Mises stress (Max. 1.46 GPa)

Z-axis displacement is uniform throughout the contact pad area

The Von Mises stress is within the elastic limit of copper with a reasonable safety margin for the desired Z-axis displacement Max. Z-axis displacement: 4.8 µm Applied force: 5 mN

### Conclusions

The design of a MEMS micropackaging system is presented that enables SoC integration. Major components of the system consist of MEMS socket submodules and insertable/removable microbus card(s). The system demonstrates advantages over conventional packaging systems in terms of: (a) easy removal or integration of a new die/device; (b) permanent or non-permanent module integration; (c) reconfigurable connectivity using microbus card, and; (d) an application specific custom packaging geometry that can be batch fabricated using MEMS technology.

### **Acknowledgements**

The research has been made possible by the interest and support provided by the Gennum Corporation of Burlington, Ontario. The authors greatly acknowledge the generous support of the following partners: CMC, MICRONET and NSERC. The Research Centre for Integrated Microsystems at the University of Windsor would like to acknowledge the access to the outstanding MEMS technology provided by the IntelliSense Corporation, 16 Upton Drive, Wilmington, MA 01887, USA as part of a collaborative partnership.

### References

- Yoshio Mita, Makoto Mita, Agnes Tixier, Jean-Phillipe Gouy and Hiroyuki Fujita, "Embedded-Mask-methods for mm-scale 1. Multilayer Vertical/Slanted Si Structures", Proceedings of MEMS 2000 Conf., Miyajaki, Japan, pp. 300-305.

- Agnes Tixier, Yoshio Mita, Satoshi Oshima, Jean-Phillipe Gouy and Hiroyuki Fujita, "3-D Microsystem Packaging for 2. Interconnecting Electrical, Optical and Mechanical Microdevices to the External World", Proc. of MEMS 2000 Conf., Miyajaki, Japan, pp. 698-703.

- 3. H. GoldStein, "Packages Go Vertical", IEEE Spectrum, August 2001, pp. 46-51.